Here’s a question from the last EMC webinar regarding “stitching capacitors” – what they are and how they’re used. While I attempted to answer the question during the Q&A session, things seemed a bit rushed, so here are some details.

A stitching capacitor provides a path for return current to flow back to it’s source. The capacitor would connect between the ground plane and power plane and must be located adjacent to where the signal trace changes reference planes. If the two planes are at the same potential, you only need to connect them together with a via at the place where the signal trace penetrates. Here’s a couple slides form my seminar that diagrams the issue. You can also run a ground trace (signal return trace through vias to do the same thing.

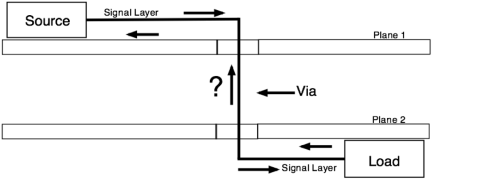

Figure 1 – Here’s one of the most common issues from a slide taken from my EMC design seminar. If a clock trace needs to penetrate through two planes, how does the return current get back to the source?

If the two planes are the same potential – for example, signal return planes – then you can merely connect the two planes together with (typically two, or more) vias on either side of the clock trace. However, if the two planes are different – for example, signal return and power – then obviously, vias would not work, so we replace them with high-frequency bypass capacitors – i.e., “stitching” capacitors – on either side of the clock trace. Unfortunately, connecting each side of the capacitor to buried layers will require multiple vias, so to keep lead/trace inductance as small as possible, the vias must be located so as to minimize trace length and should be located as close as possible to the source clock trace penetration.

Stitching capacitors may also be used to provide a high-frequency connection across isolated planes, but this is a more advanced technique we can discuss at a later time.